Page 3 of 6

Re: New XMOS chips??!

Posted: Tue Mar 24, 2015 8:04 pm

by richard

infiniteimprobability wrote:There are a few other instructions which will boost speed too - especially load/store double (64b). This will really help on memcpy, dsp and push/pops.

To make this a bit more concrete, using memcpy to copy 1KB of word aligned data from one location to another is 2.55 times faster on xCORE-200 (assuming at least 5 cores are in use). The speed up comes from the use of double word load and store instructions, dual issue and increased instruction fetch bandwidth.

Re: New XMOS chips??!

Posted: Wed Mar 25, 2015 12:26 am

by segher

I assume that 2.55x speedup is from 1-lane mode to 2-lane

mode, both on 200 parts? So that makes 2.04x speedup

over G/L (assuming max. 5 threads). G/L can do the loop

in 4 thread cycles, so 1 byte per thread cycle (no loop

unrolling); 200 can do it 2 bytes per thread cycle? Nice :-)

Re: New XMOS chips??!

Posted: Wed Mar 25, 2015 12:04 pm

by Folknology

XMatt wrote:Folknology wrote:Thanks Xmatt

Does the boot actually use QSPI to improve performance as well as overlays?

Yes QSPI boot, the embedded flash parts have QSPI flash internally.

Thanks XMatt does this mean that the X*F chips (with internal flash) are based on a Quad SPI tile bonded to ports 1B,4B & 1C. If so can these pins be used externally, or is something more sophisticated happening?

I am trying to work out if I can use these pins as I would like to be able to.

regards

Al

Re: New XMOS chips??!

Posted: Wed Mar 25, 2015 3:18 pm

by richard

segher wrote:I assume that 2.55x speedup is from 1-lane mode to 2-lane

mode, both on 200 parts? So that makes 2.04x speedup

over G/L (assuming max. 5 threads). G/L can do the loop

in 4 thread cycles, so 1 byte per thread cycle (no loop

unrolling); 200 can do it 2 bytes per thread cycle? Nice :-)

The 2.55x speed up compares an optimized dual issue memcpy running on a xCORE-200 logical core to an optimized single issue memory running a XS1-L/G logical core assuming that the logical cores are running at the same rate. If you have 5 or more cores active then the cores will be running at the same rate. If have less than 4 cores active the xCORE-200 cores will be running at 100MHz instead of 125MHz so the speed up will only be 2.04x.

Re: New XMOS chips??!

Posted: Wed Mar 25, 2015 5:10 pm

by segher

Ah, you're talking about a full C library memcpy routine,

so that includes setup overhead etc.

We don't have manuals yet so I have to guess a bit; a fun

game :-)

Looking only at the core of an unrolled copy loop, on L/G

that is [ load / store / fetch no-op ], so 3 cycles per word,

12 cycles for 4 words. To get about 2.55x speedup over

that, my best guess is 2.4x, via [ ll / ss / ll / ss / fetch ].

Is that about right?

Pretty awesome :-)

Re: New XMOS chips??!

Posted: Thu Mar 26, 2015 12:16 pm

by leon_heller

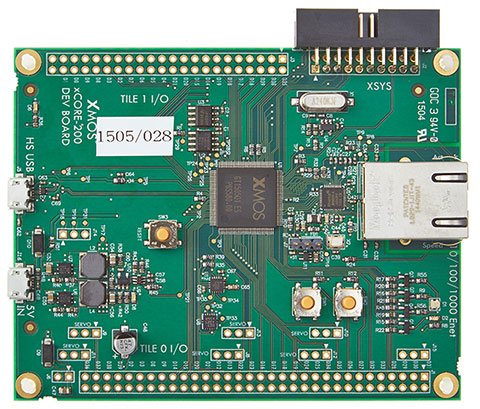

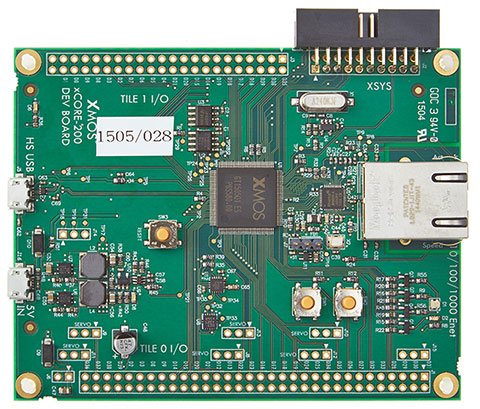

A low-cost kit should soon be available:

https://www.xmos.com/support/boards?pro ... 0&secure=1

Version 14.0 of xTIMEcomposer Studio, which supports the new devices, is available now:

http://www.xmos.com/support/tools

The Timing Analyser can be used to check performance details.

Re: New XMOS chips??!

Posted: Tue Mar 31, 2015 5:33 pm

by lilltroll

I got the

today.

Anyone else?

I'm playing around with the gigabit Ethernet example and virtual COM port here :)

Re: New XMOS chips??!

Posted: Tue Mar 31, 2015 7:40 pm

by leon_heller

How did you get it?

Re: New XMOS chips??!

Posted: Wed Apr 01, 2015 5:09 pm

by segher

lilltroll wrote:I got the [nice new board] today.

Anyone else?

With cables! :-)

Re: New XMOS chips??!

Posted: Wed Apr 08, 2015 8:09 am

by Hagrid

So, can anyone tell me how to get one of these boards? Pricing?

Cannot find any listing on Element14/Farnell or Digikey.