Page 2 of 2

Re: Programming programmable clock

Posted: Wed Aug 17, 2016 10:29 pm

by mon2

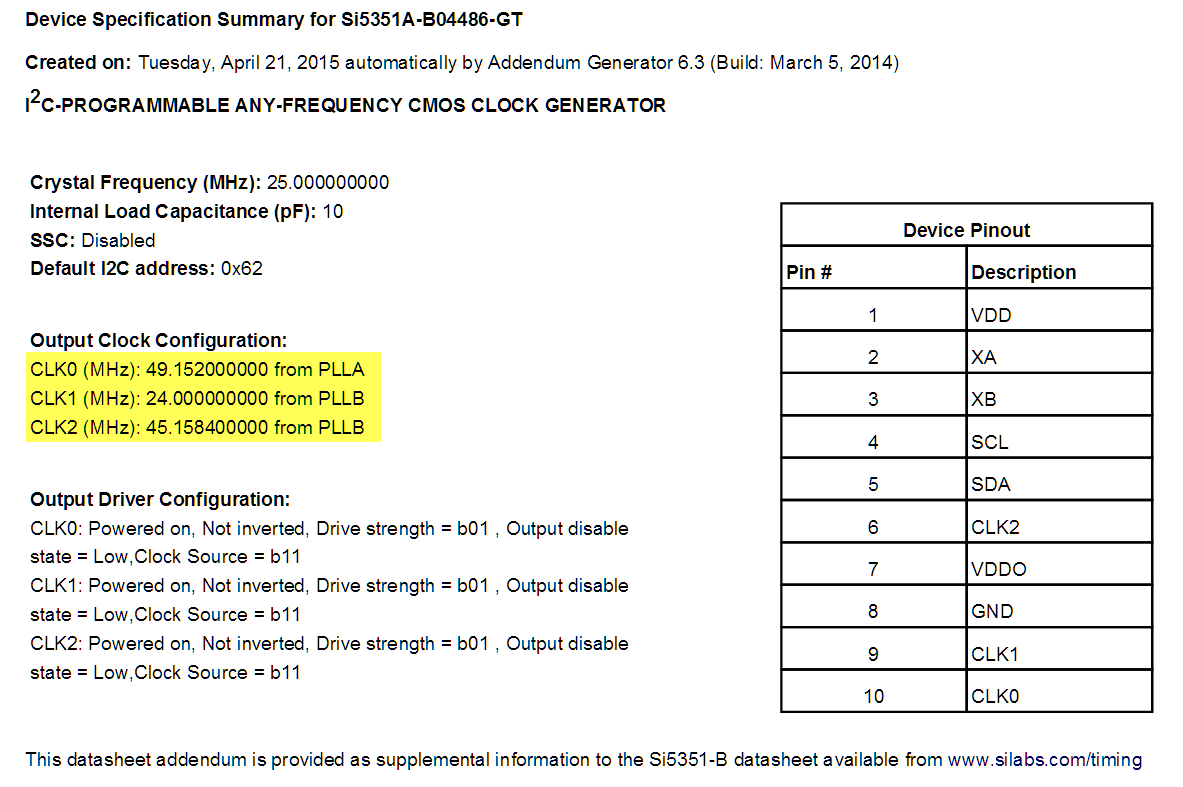

For some closure to this thread and more for future readers, SiLabs distributors are carrying a pre-programmed version of this PLL as follows:

Mfr P/N SI5351A-B04486-GT

http://www.digikey.com/product-detail/e ... ND/5799560

Re: Programming programmable clock

Posted: Thu Jan 18, 2018 4:14 am

by 1codis

This is the oscillator that the dev board for the XHRA-2HPA uses, but it seems like the frequencies are exactly twice what they need to be in order to drive MCLK and a typical DAC. Can damage be done to the chip by driving it at the default frequencies (~49MHz)?

Re: Programming programmable clock

Posted: Thu Jan 18, 2018 4:51 pm

by mon2

The Sabre 9018 DAC (SABRE9018Q2C) used on the XRHA-2HPA board is noting that MCLK can be upto 100 Mhz.

Here is a URL for the datasheet for your review:

https://myl8test.files.wordpress.com/20 ... t-here.pdf

Re: Programming programmable clock

Posted: Thu Jan 18, 2018 5:38 pm

by akp

The ADC I'm working with can use an MCLK up to 49.152MHz so this part would be useful. I suspect with this PLL you will have an analog switch to select between 48kHz and 44.1kHz families. If you absolutely need 1/2 those rates, and you have plenty of clock blocks on the XMOS chip, I suspect you could take the high frequency clock and divide it by 2 on your XMOS chip and output that as the board MCLK.