I am new to XMOS, but think it's a great architecture. I am trying to get my first project built.

Using a clocked output, how do I start the first rising clock edge only after there is valid data? Here is my test code:

-----------------------------

#include <xs1.h>

out port outP = XS1_PORT_1F ;

out port outClock = XS1_PORT_1D ;

clock clk = XS1_CLKBLK_1 ;

int main ( void ) {

configure_clock_rate (clk, 100, 8);

configure_out_port (outP, clk, 0);

configure_port_clock_output (outClock, clk);

outP <: 1;

start_clock (clk);

while (1) {

outP <: 0;

outP <: 1;

}

}

-----------------------------

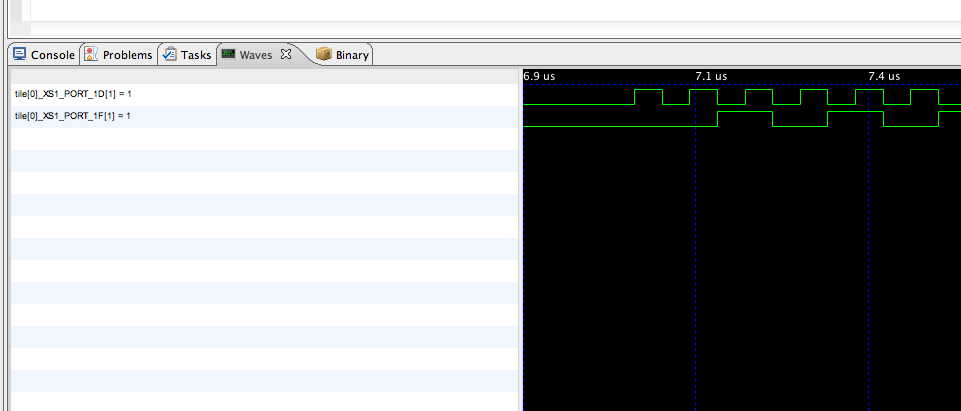

I am trying to start the clock after outP has gone high. When I run this in the simulator, I get the following trace:

As you can see, there are two rising clock edges before outP (port 1F) goes high. This won't work for my system, because the chip I am talking to will clock in garbage and be out of sync with the data. I need to have the clock start when the data is valid. How can I do this?

Any help in the next few hours would be greatly appreciated! ;-)