Code: Select all

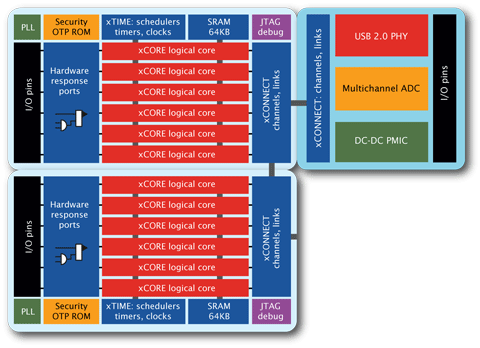

<Node Id="1" InPackageId="1" Type="periph:XS1-SU" Reference="usb_tile">I've read the XN specification which states that this means this type of a Node is an XS1-SU peripheral node. OK, great. But what is an XS1-SU? According to the XMOS product catalog, an XS1-SU is a completely separate microcontroler with a single ARM core. That doesn't make sense to me in this context since this XN file is descriping a single, different chip.

Since the XS1-U8A-64 has what appears to be a separate tile which contains the USB PHY and some other goodies, does this Node declaration allow the general purpose tile with 8 cores to communicate to the tile with the USB PHY and other things located there?

I've read a lot of documentation on XMOS and this nomenclature isn't very obvious to me. If there is something I missed or some documentationm that someone can point me to, that would be very helpful.

Thanks!