Ooh nice. Anything else new wrt ports? A usable cross-thread

PEEK, O/D on multibit ports, anything else?

i2c signalling?

-

segher

- XCore Expert

- Posts: 844

- Joined: Sun Jul 11, 2010 1:31 am

-

infiniteimprobability

Verified

Verified - XCore Legend

- Posts: 1177

- Joined: Thu May 27, 2010 10:08 am

It's not just related to ports, but on xCORE 200 you can now divide down an external clock (1b port input to clock block), rather than having to do the buffered port clock stream trick..Ooh nice. Anything else new wrt ports? A usable cross-thread

PEEK, O/D on multibit ports, anything else?

-

babazaroni

- Experienced Member

- Posts: 94

- Joined: Sun Feb 10, 2013 4:47 am

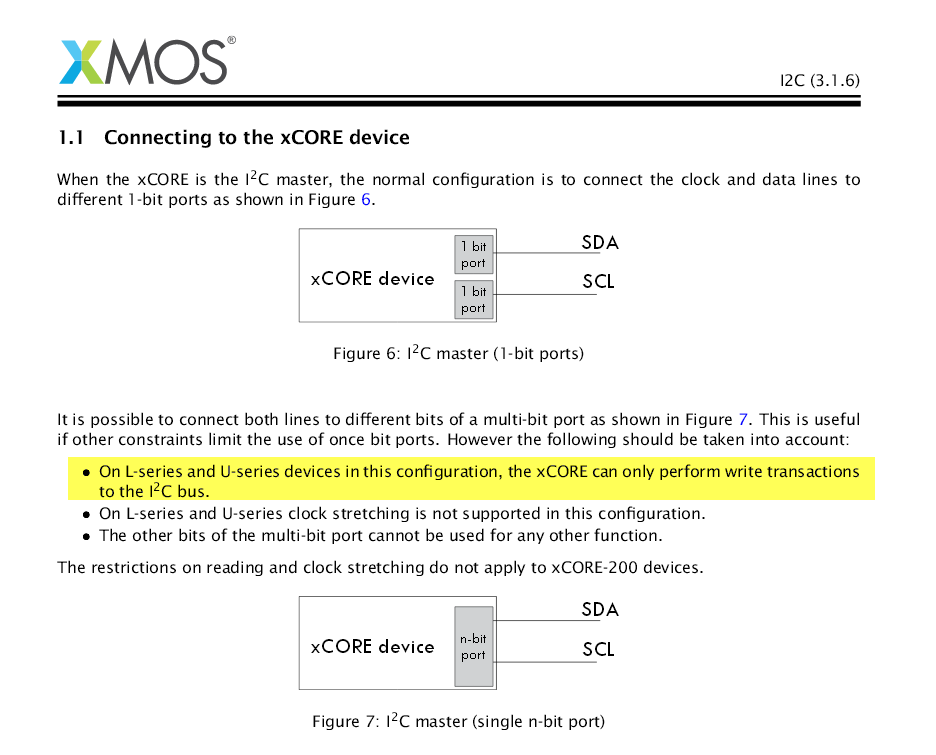

Good to hear about the 200 and open drain ports. This is a feature found on a lot of micros for quite a few years. This will allow I2C to be put on a 4bit port with no loss of capabilities, freeing up the valuable 1-bit ports

Speaking of I2C, I hope Xmos will have an integrated master/slave I2c library eventually, also found on many micros for many years.

There is some slave code available from an FAE but it's not integrated with master. I2C is very elegant to include the ability for a master to transmit, while at the same time another micro is treating the master as a slave. Depending on the arbitration, one of the masters will give up and resume the rest of the sequence as a slave. This can't happen if master and slave code are not integrated, as is the current situation. I'm writing my own solution.

Speaking of I2C, I hope Xmos will have an integrated master/slave I2c library eventually, also found on many micros for many years.

There is some slave code available from an FAE but it's not integrated with master. I2C is very elegant to include the ability for a master to transmit, while at the same time another micro is treating the master as a slave. Depending on the arbitration, one of the masters will give up and resume the rest of the sequence as a slave. This can't happen if master and slave code are not integrated, as is the current situation. I'm writing my own solution.

-

Hagrid

- Active Member

- Posts: 44

- Joined: Mon Jul 29, 2013 4:33 am

Does the figure in the XCORE Architecture Flyer in the Hardware Response(TM) Port section reflect this capability?infiniteimprobability wrote:It's not just related to ports, but on xCORE 200 you can now divide down an external clock (1b port input to clock block), rather than having to do the buffered port clock stream trick..Ooh nice. Anything else new wrt ports? A usable cross-thread

PEEK, O/D on multibit ports, anything else?

Would love to see an accurate (and fully labelled) diagram of the clock block and ports. This is for the purpose of preparing training materials.

-

Folknology

- XCore Legend

- Posts: 1274

- Joined: Thu Dec 10, 2009 10:20 pm

BTW babazoroni the new Xmos 'i2c_lib' implements both master and slave, synchronous and asynchronous you really should check it out.babazaroni wrote: ..

Speaking of I2C, I hope Xmos will have an integrated master/slave I2c library eventually, also found on many micros for many years.

..

-

babazaroni

- Experienced Member

- Posts: 94

- Joined: Sun Feb 10, 2013 4:47 am

Thanks Folknology for the heads up. I did look at the docs for the new I2C library.

It does not support multi-master which is what I also need.

It also seems to require 2 cores to implement slave and master running together.

Too bad, since it's quite easy to do multi-master arbitration and also master/slave in a single core.

I'll have to stick with my version for now.

It does not support multi-master which is what I also need.

It also seems to require 2 cores to implement slave and master running together.

Too bad, since it's quite easy to do multi-master arbitration and also master/slave in a single core.

I'll have to stick with my version for now.

-

goodfeather

- Member++

- Posts: 23

- Joined: Wed Mar 30, 2016 11:10 am

Dear Sirs,

After studying your discussion, I still do not know the reason why XS1 "module_i2c_single_port" can not perform reading registers from the slave device.

Could you please give me more details?

Thanks

After studying your discussion, I still do not know the reason why XS1 "module_i2c_single_port" can not perform reading registers from the slave device.

Could you please give me more details?

Thanks

-

mon2

- XCore Legend

- Posts: 1913

- Joined: Thu Jun 10, 2010 11:43 am

Hi goodfeather.

What are the issues you are facing ? What are the details of your project ? Slave device details ?

Do you have the required pull-up resistors to +3v3 for I2C communication ?

The I2C library does work well. Here is a post where we tested the XMOS StartKit as an I2C master working with the SiLabs Si5351A PLL as the slave. See page 2 of this thread for the full source code which you should be able to modify very quickly to support your target I2C slave address:

http://www.xcore.com/forum/viewtopic.ph ... 1&start=10

Kumar

What are the issues you are facing ? What are the details of your project ? Slave device details ?

Do you have the required pull-up resistors to +3v3 for I2C communication ?

The I2C library does work well. Here is a post where we tested the XMOS StartKit as an I2C master working with the SiLabs Si5351A PLL as the slave. See page 2 of this thread for the full source code which you should be able to modify very quickly to support your target I2C slave address:

http://www.xcore.com/forum/viewtopic.ph ... 1&start=10

Kumar

-

goodfeather

- Member++

- Posts: 23

- Joined: Wed Mar 30, 2016 11:10 am

Dear Kumar,

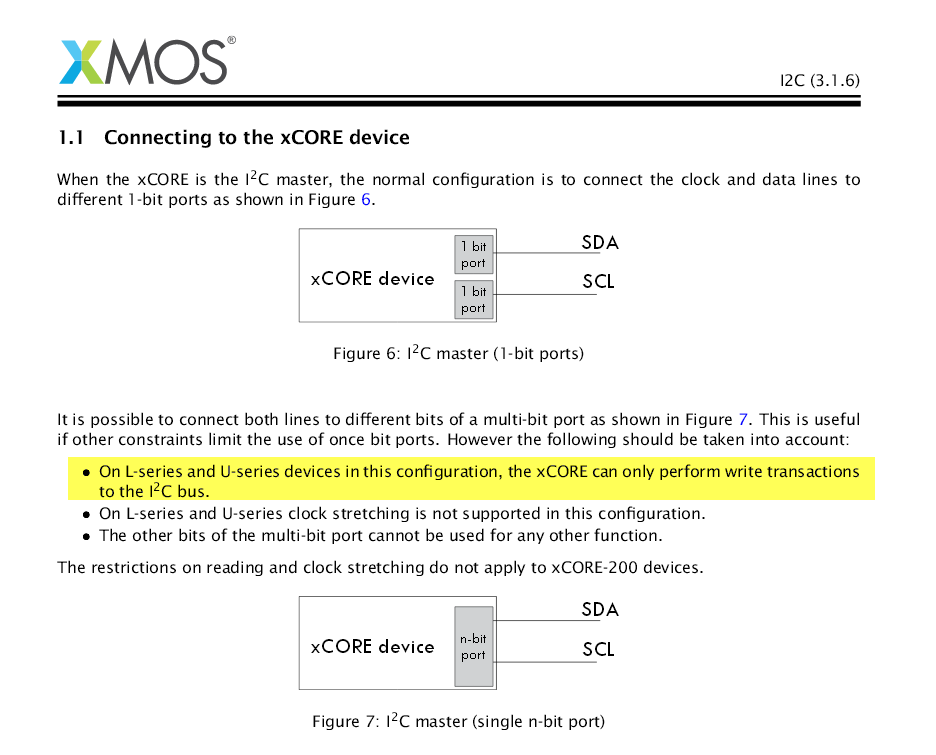

I plan to use single port I2C design instead of two 1-bit ports.

But after reading "module_i2c_single_port" and "lib_i2c3.1.6"source code, I found XS1 can not perform reading registers from the slave device under these modules.

To my understanding, if XS1 master could peek ACK from slave device, it also can peek data from slave.

Why not?

Thanks

I plan to use single port I2C design instead of two 1-bit ports.

But after reading "module_i2c_single_port" and "lib_i2c3.1.6"source code, I found XS1 can not perform reading registers from the slave device under these modules.

To my understanding, if XS1 master could peek ACK from slave device, it also can peek data from slave.

Why not?

Thanks

-

mon2

- XCore Legend

- Posts: 1913

- Joined: Thu Jun 10, 2010 11:43 am

Ok, after some digging, found the same notice you raised:

Is this for a new design ? Perhaps plan to allocate 2 single bit ports for I2C ?

The XCORE-200 series CPU do not have this restriction ? Move to use the XCORE-200 series devices ?

Yup, this thread confirms that XCORE-200 works as you are requesting:

https://www.xcore.com/forum/viewtopic.php?f=3&t=2033

Is this for a new design ? Perhaps plan to allocate 2 single bit ports for I2C ?

The XCORE-200 series CPU do not have this restriction ? Move to use the XCORE-200 series devices ?

Yup, this thread confirms that XCORE-200 works as you are requesting:

https://www.xcore.com/forum/viewtopic.php?f=3&t=2033