So this is the first XMOS chip circuit I've "designed" (ie: heavily cribbed from other designs and stuffed together in a manner that might even work). I'm well aware of my limitations as a PCB designer (more of a software guy :), so if anyone would be good enough to give this a once-over and make sure I'm not doing anything *too* egregious, I'd really appreciate it.

The goal is to take a parallel-bus (at a relatively low frequency), serialise it to reduce the wire-count, and send changes over an xconnect link via cat-6 RJ45. That second XMOS chip will de-serialise the bus data and present it to clients as if they were connected directly to the original parallel bus. I won't go into more detail on the second chip and returned data because the circuit here is just the host-side.

In addition, the host side XMOS gets to expand the RAM of the host computer, by taking over the parallel bus and exposing its SDRAM in banks of mapped memory, and it provides a "hard drive" via an SD-card.

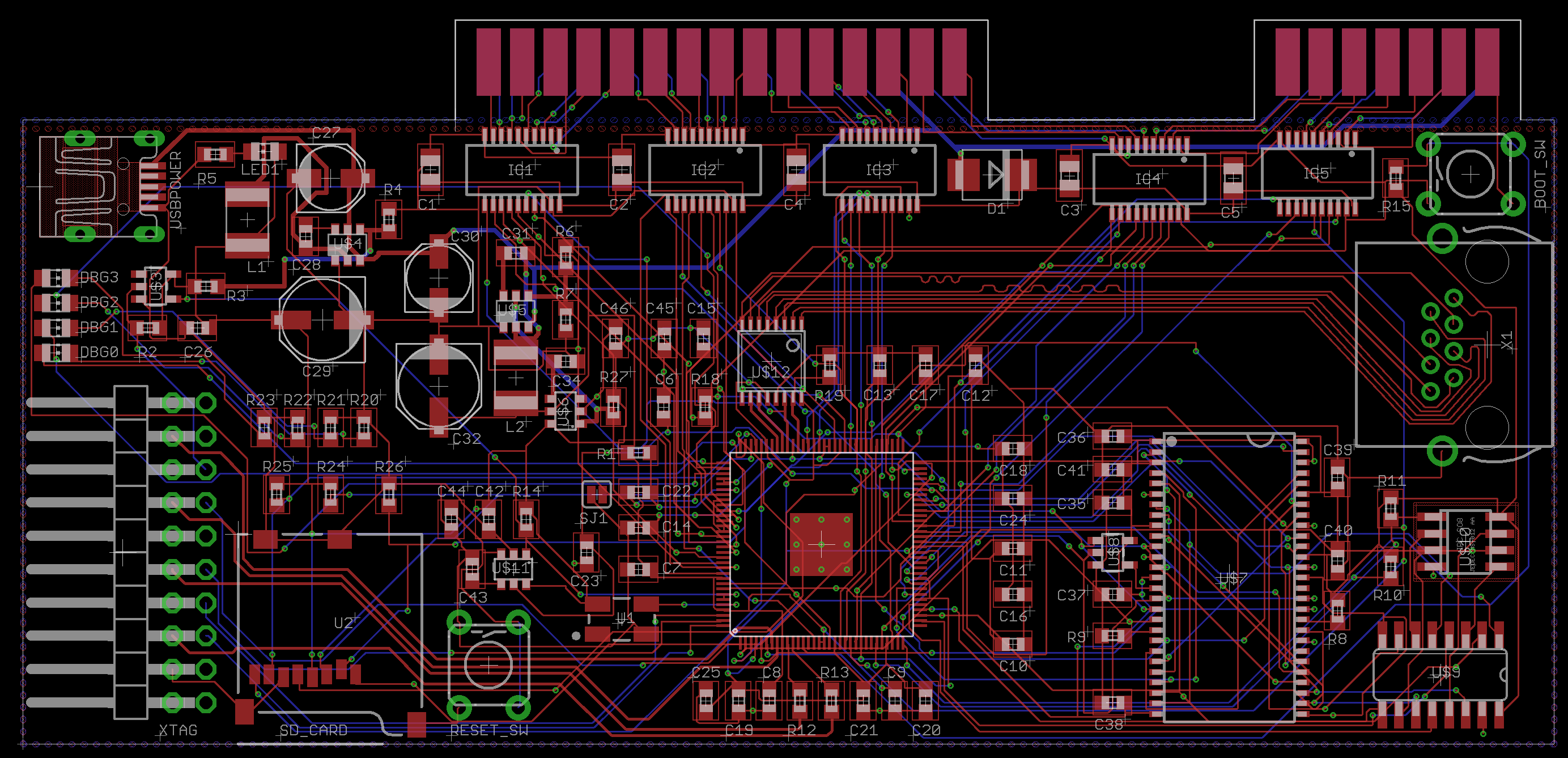

With that said, here's the schematic pages:

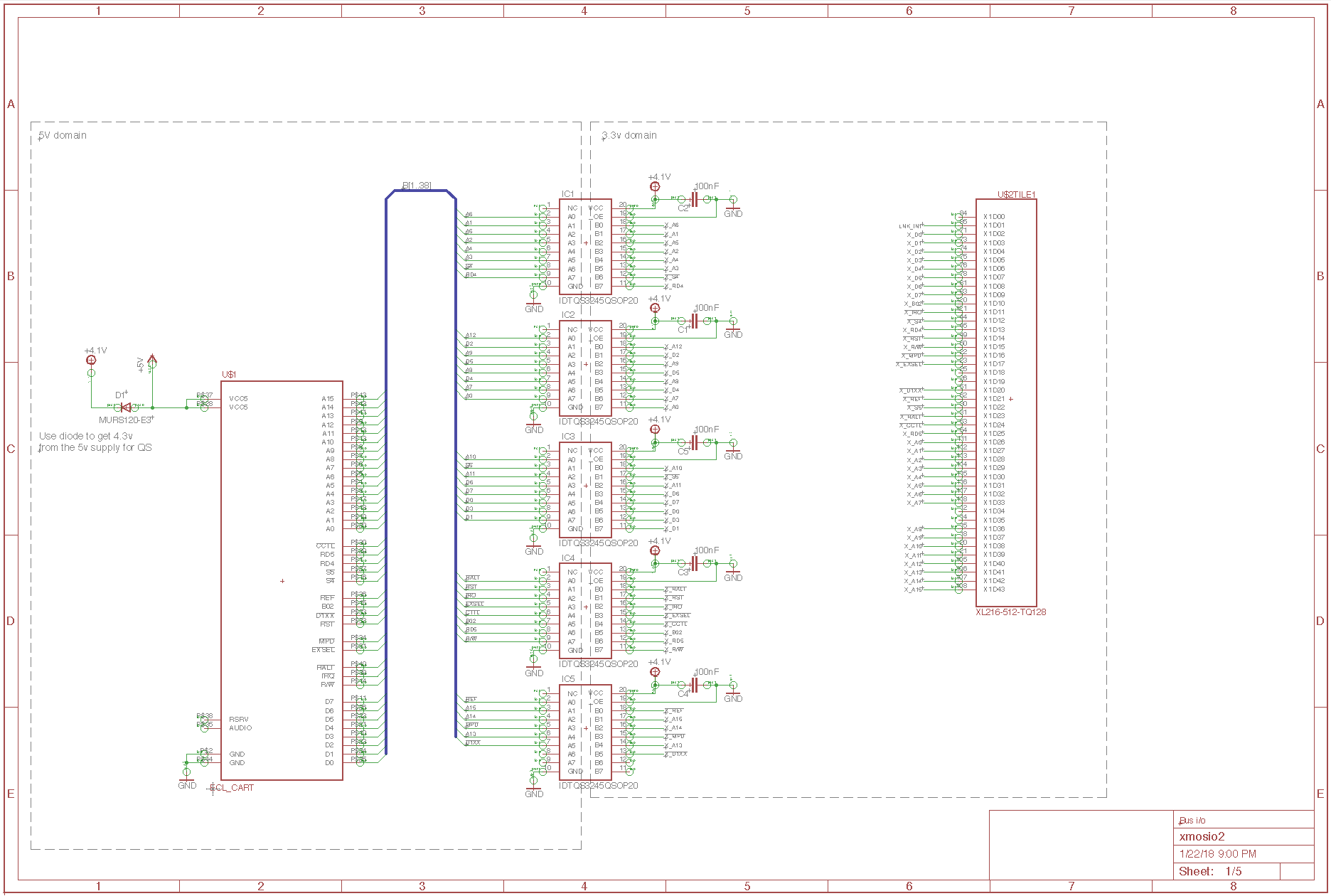

1: The host<==>XMOS parallel bridge

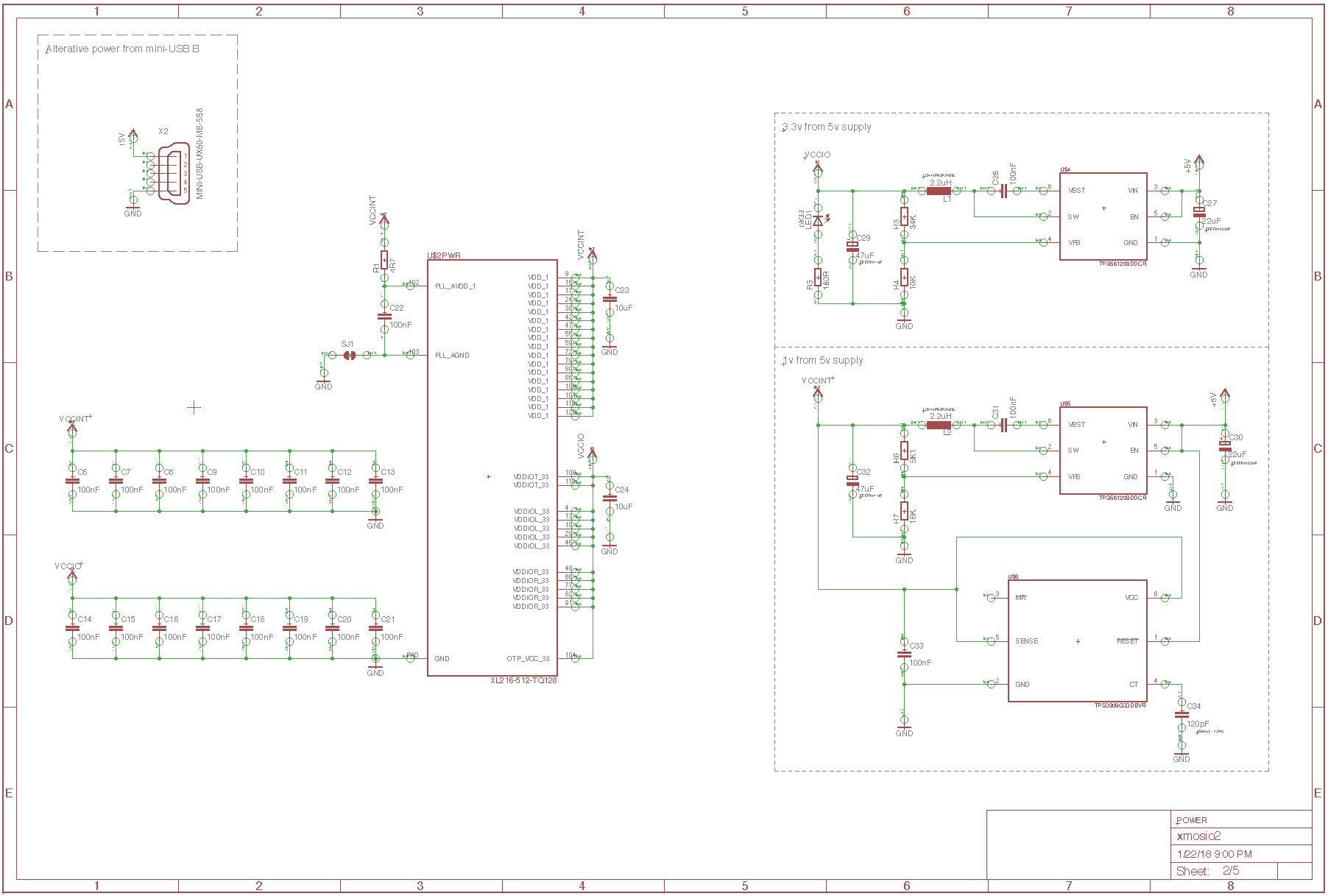

2: The power sequencing and voltage lines

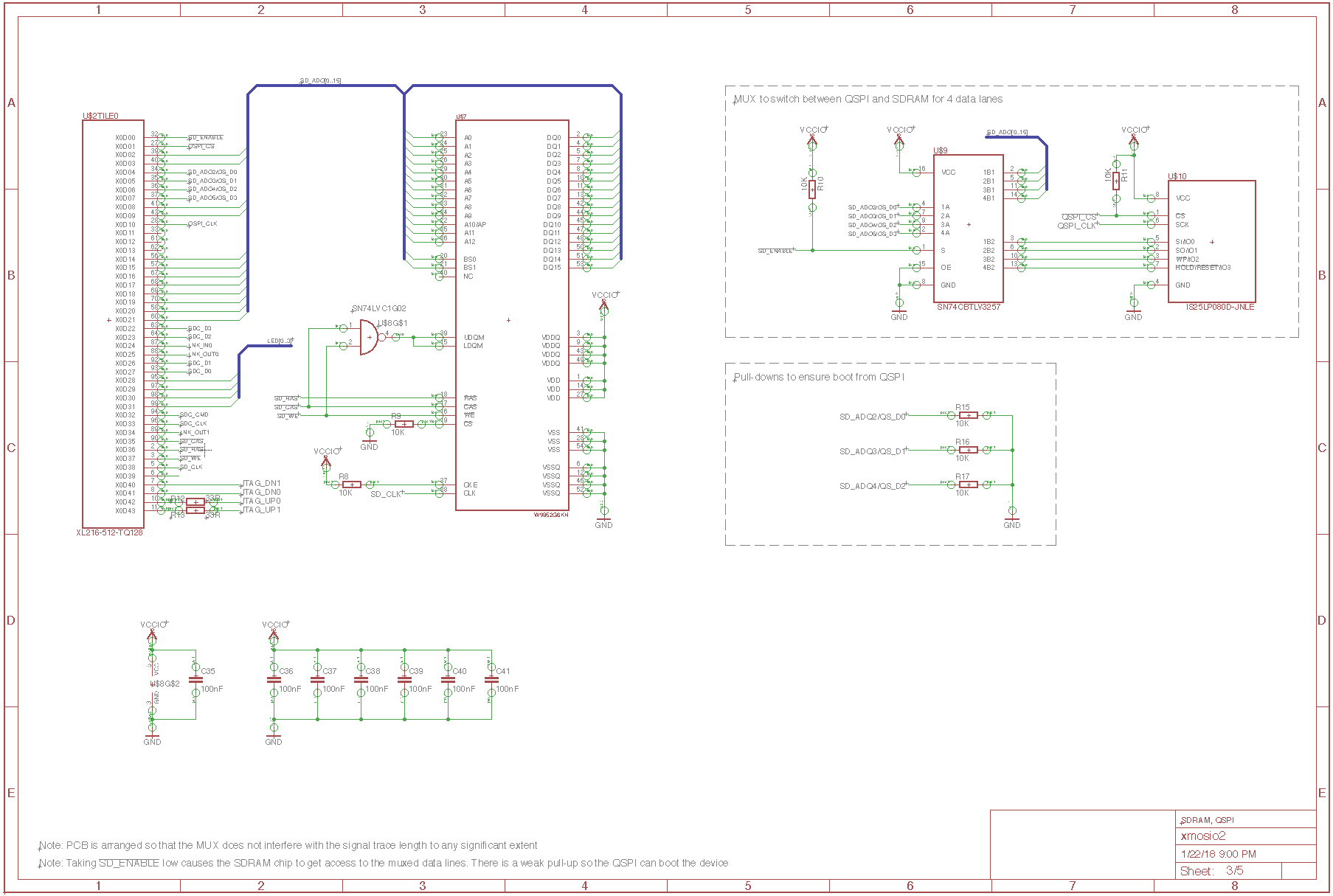

3: External memory (QSPI for boot, SDRAM for memory expansion)

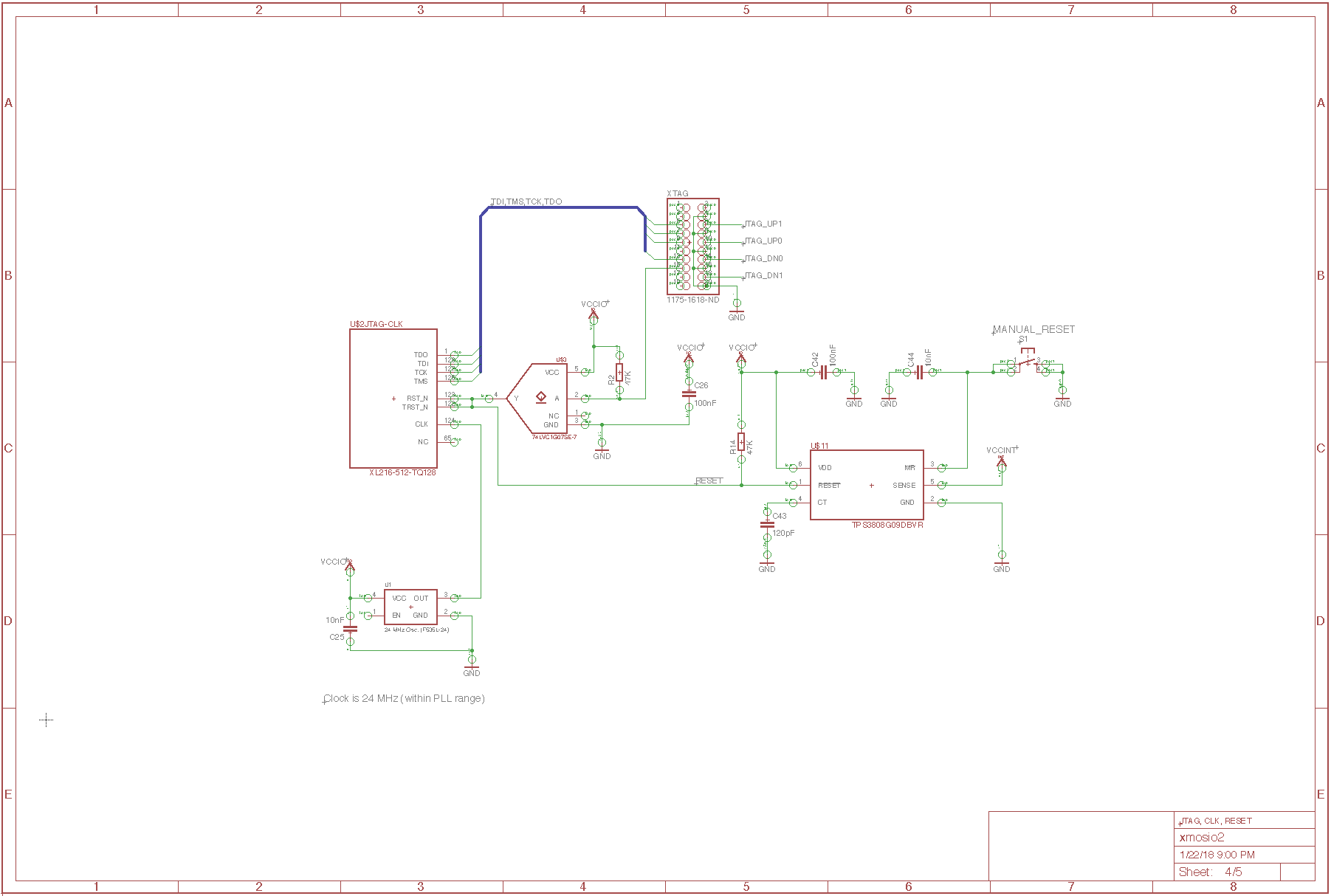

4: Clock and JTAG connection:

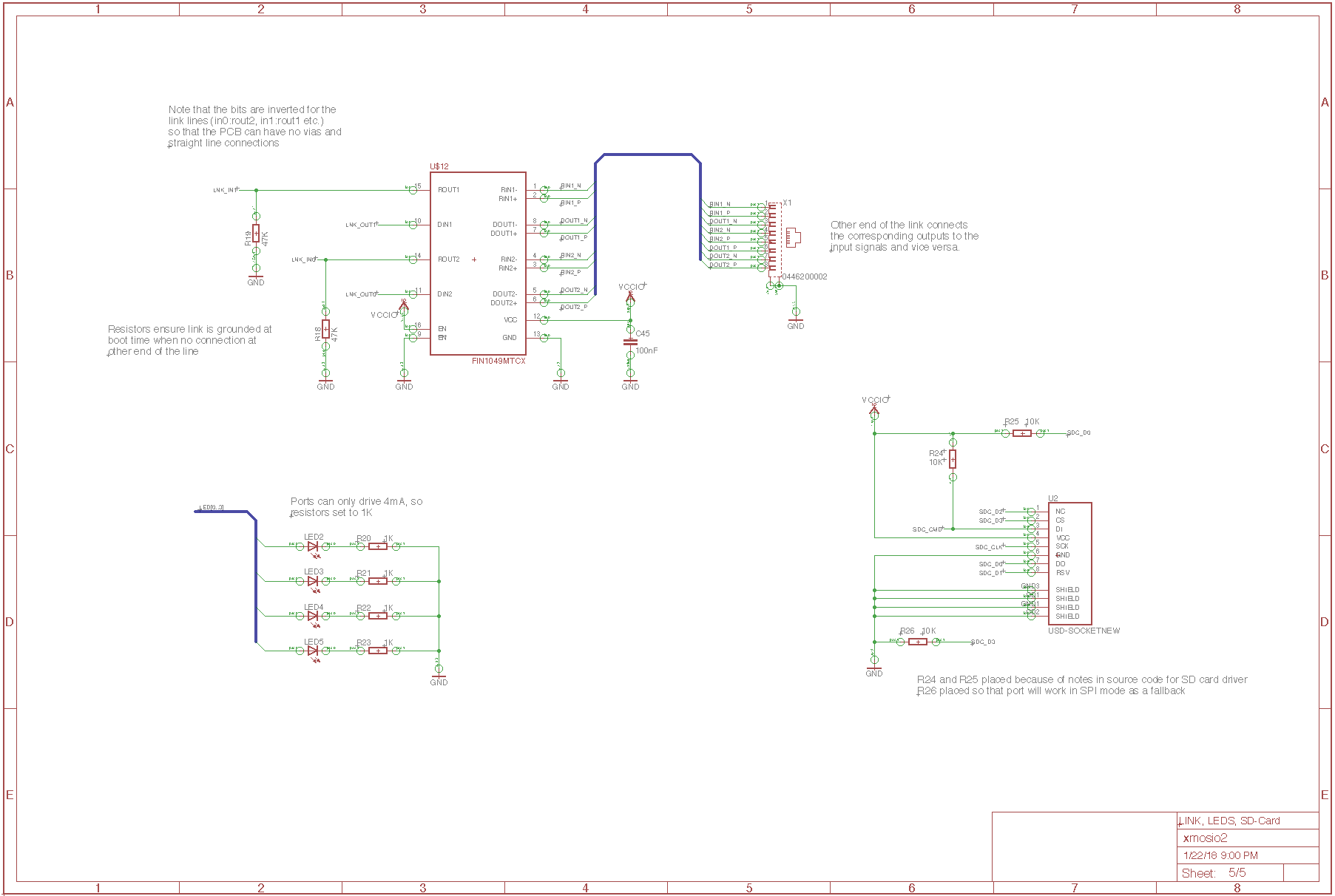

5: Link off-board, LEDs and 4-bit SD-card interface

In addition, here's the PDF of the above, for easier viewing.

Questions I'm particularly interested in getting answers to

- You can see in schematic 1/5 that the host side is 5v logic, and I'm using quick-switches to switch the logic level down to a more palatable 3.3v. I'm using a diode to convert the 5v down to 4.3v because I think there's a 1v drop within the quick-switch, which gives me a final voltage of 3.3v - can anyone who's done this confirm this actually works ? I really don't want to blow up the XMOS chip at power-on...

- I'm also a bit nervous about the power-supplies. I've taken this from this project so I'm hopeful it'll work, but if anything jumps out at anyone, I'm all ears :)

- On a general note, I've been using 10k for pull-down/pull-ups, for example on sheet 3/5 where the XMOS is set to boot from QSPI because X0D0{4,5,6} are all pulled low with a 10k pull-down. Is that an ok value ? Not too weak ?

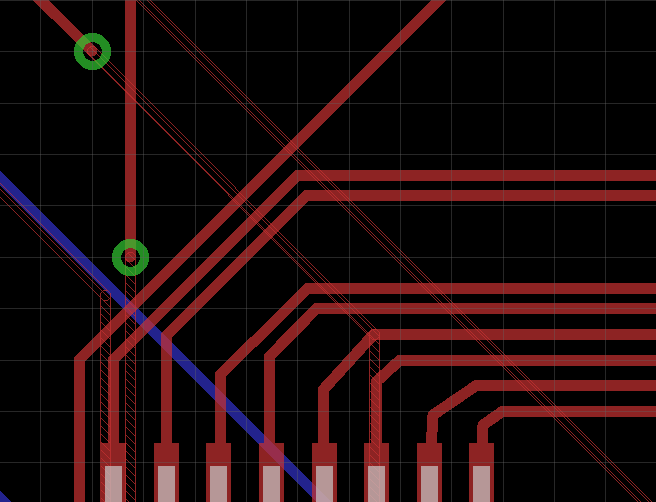

- I haven't attached a UART to the design because I'm hoping to use the XDebug interface on the XTAG connection. I'm using a 2-bit X0L0 link with 33R resistors on the drivers (out signals). On the PCB, these (together with the Link->differential-driver->RJ45) are the first-routed wires, are length-matched, have no vias and run over the ground plane. Is there anything else I ought to be looking out for ?

- On sheet 5, the SD-card interface is laid out. The source for the SD-card 4-bit driver mentions that SDC_CMD and SDC_D0 ought to have pull-ups. The same question regarding suitability of the 10K applies here.

- I'm also hoping to be able to fall-back to the 1-bit SPI mode, in which SDC_D3 operates as a /CS signal. I've put a weak pull down (again, 10K) to GND on that line. Is that likely to impact the 4-bit mode too much ? ie: Am I trying to have my cake and eat it here ?

Cheers

Simon