I have an xCORE-200 USB sliceKIT and am trying to get the SDRAM slice card to work with a small demo program of my own. Here's the code:

Code: Select all

/*

* SDRAM Playground.xc

*

* Created on: Mar 25, 2016

* Author: Amandio

*/

#include <platform.h>

#include <xs1.h>

#include "sdram.h"

#include "memory_address_allocator.h"

#include <stdio.h>

#define BUFFERSIZE 1024

#ifndef SDRAMTILE

#define SDRAMTILE tile[1]

#endif

on SDRAMTILE: out buffered port:32 sdram_dq_ah = XS1_PORT_16A;

on SDRAMTILE: out buffered port:32 sdram_cas = XS1_PORT_1B;

on SDRAMTILE: out buffered port:32 sdram_ras = XS1_PORT_1G;

on SDRAMTILE: out buffered port:8 sdram_we = XS1_PORT_1C;

on SDRAMTILE: out port sdram_clk = XS1_PORT_1F;

on SDRAMTILE: clock sdram_cb = XS1_CLKBLK_1;

int CompareMovableBuffer( unsigned * movable buffer, unsigned * bufferCopy, unsigned length){

for ( int i = 0; i < length; i++){

if(buffer[i] != bufferCopy[i]){

printf("buffer[%d] = %d bufferCopy[%d] = %d\n", i, buffer[i], i, bufferCopy[i]);

return 0;

}

}

return 1;

}

void app(streaming chanend c_sdram, client interface memory_address_allocator_i mem_alloc){

s_sdram_state sdram_state;

sdram_init_state(c_sdram, sdram_state);

unsigned buffer[BUFFERSIZE];

unsigned bufferCopy[BUFFERSIZE];

unsigned * movable buffer_pointer = buffer;

unsigned seed = 98;

unsigned base_address;

mem_alloc.request((BUFFERSIZE * sizeof(unsigned)), base_address);

unsigned result = sdram_read(c_sdram, sdram_state, base_address, BUFFERSIZE, move(buffer_pointer));

sdram_complete(c_sdram, sdram_state, buffer_pointer);

for (int i = 0; i < BUFFERSIZE; i++){

seed %= 0xFFFF;

buffer_pointer[i] = seed;

bufferCopy[i] = seed;

crc32(seed, 77, 9890);

}

result = sdram_write(c_sdram, sdram_state, base_address, BUFFERSIZE, move(buffer_pointer));

sdram_complete(c_sdram, sdram_state, buffer_pointer);

for (int i = 0; i < BUFFERSIZE; i++){

buffer_pointer[i] = 0;

}

result = sdram_read(c_sdram, sdram_state, base_address, BUFFERSIZE, move(buffer_pointer));

sdram_complete(c_sdram, sdram_state, buffer_pointer);

if (CompareMovableBuffer(move(buffer_pointer), bufferCopy, BUFFERSIZE)) printf("Arrays MATCH!\n");

else printf("Arrays DO NOT MATCH!\n", BUFFERSIZE);

while(1);

}

int main(){

streaming chan c_sdram[1];

interface memory_address_allocator_i mem_alloc_i[1];

par{

on SDRAMTILE: sdram_server(c_sdram, 1,

sdram_dq_ah,

sdram_cas,

sdram_ras,

sdram_we,

sdram_clk,

sdram_cb,

2, 128, 16, 8, 12, 2, 64, 4096, 4); // I don't know what these integer arguments mean yet.

on SDRAMTILE: memory_address_allocator(1, mem_alloc_i, 0, 1024*1024*8);

on SDRAMTILE: app(c_sdram[0], mem_alloc_i[0]);

}

}

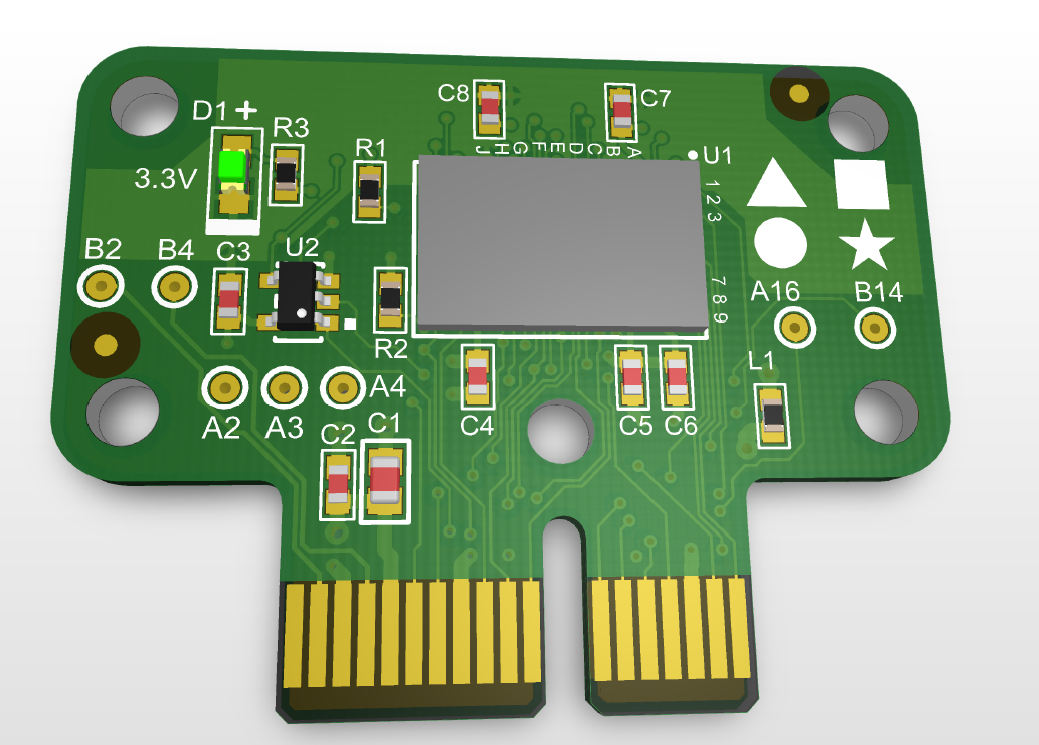

Here's a picture of my setup:

[thumbnail]https://www.anony.ws/i/2016/03/29/0329161643.jpg[/thumbnail]

I've got the SDRAM sliceCard connected to the Type 3/7 connector and I have the jumper on J14 across pins 1 and 2. In the code above I've place all port definitions and tasks in tile 1 since that is where the pins on the Type 3/7 connector map to.

My problem is that if I define BUFFERSIZE to anything greater than 13, I start to see differences in the array read back from the SDRAM slice card. For example, if I define BUFFERSIZE to be 14, then the last index fails the match. If I define it to be 1024, I can see that some inidices after a certain point contain garbage values but eventually pick up from where they left off so it looks like indices that do match are now offset.

I uploaded the project to my Google Drive if anyone wants to take a look at it:

SDRAM_Playground

I'm using lib_sdram v3.0.2. I followed along the lib_display_controller which uses sdram heavily as guidance. I couldn't find anything too different in how it is accessing the sdram server.

Has anyone had much luck and/or experience using the SDRAM sliceCard who can give me some pointers?

Thanks!