Using XMOS PLL to produce clock for another device

-

xlordofpainx

- Experienced Member

- Posts: 78

- Joined: Thu Mar 08, 2018 2:44 pm

Using XMOS PLL to produce clock for another device

Can I use the XE216-512-tq128 to generate the clock needed for another chip?. 45.1584-49.152 is what I need for another chip and instead of having a crystal for it I'd like to use the XMOS internal PLL and output a clock on a free pin (for example). The TX_CLK in my case is free as i will not be using ethernet so i looked into the xCORE-200 Clock Frequency Control document, but did not find specific information on changing just the RGMII clock used for TX_CLK. I could also be completely misunderstanding the whole concept.

-

xlordofpainx

- Experienced Member

- Posts: 78

- Joined: Thu Mar 08, 2018 2:44 pm

After scanning on the Forum i Stumbled upon a topic in which this is discussed- http://www.xcore.com/viewtopic.php?f=7& ... PLL#p28815. The Output of the conversation is that a clock can be put on a pin and the maximum can be up to 250MHz. but I am still do not see if i can get 49.152 from a 25Mhz clock input and also how many separate clock i could generate with the internal PLL. I know that there are 6 clock blocks per tile, but the topics on clock blocks and PLL in the documentation are a bit far a part and don't cross reference each other which confuses me to a point that I can only assume how this works and I need a more stable answer so i can design my schematic right. I will keep posting info as someone could find it useful in the future.

-

mon2

- XCore Legend

- Posts: 1913

- Joined: Thu Jun 10, 2010 11:43 am

Hi. Have not reviewed the details of the XMOS PLL but:

a) if this external clock is fixed and you do not have any plans to change this value then the best solution is to apply a small footprint, low cost fixed SMD oscillator. From our last review, the 3225 SMD oscillator is the most practical due to the volume of sales. You should be paying around $0.30-$0.40 USD per oscillator in 1k pieces out of Shenzhen, CN. Check WTL as one quality vendor:

b) alternate options are to create a pierce oscillator using a local single gate buffer + a low cost crystal. However, from an automated production point of view, you will pay more in labor costs to stuff the xx # of parts for this discrete oscillator rather than the single placement cost for the complete SMD oscillator. Also, the PCB real estate will be larger for the discrete oscillator design. Something to note.

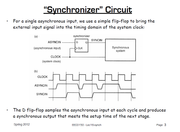

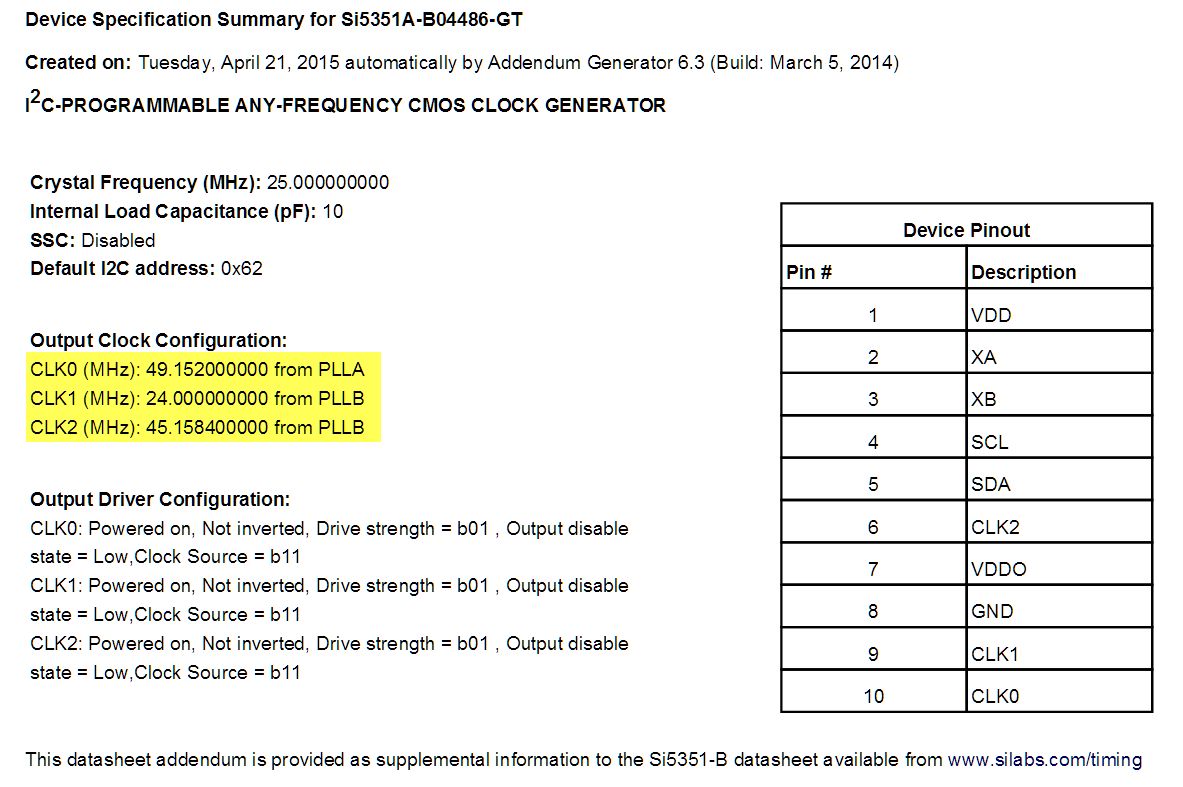

c) personally, we love the use of the Silabs Si5351A PLL which accepts a low cost 25 Mhz crystal (note that it is a crystal) and using I2C, you can dial up ANY clock you wish.

XMOS has already generated a fixed part with the same target clock output for audio projects:

https://www.digikey.com/products/en?key ... 4486-GT%20

If you purchase this exact p/n, CLK0 = 49.152 Mhz upon power up. No programming required.

You can find full source code for the use of the Si5351A PLL from here:

http://www.xcore.com/viewtopic.php?t=4647&start=10

NB: You only need the source code if you plan to change the power up value of this pre-programmed PLL. Otherwise, CLK0 will power up @ 49.152 Mhz.

The older clock builder tool is a gui tool -> select the 10 pin device -> select 25 Mhz crystal (we sourced these from WTL as well and are around $ 0.12 USD or lower) -> enter your target clock. Select Generate.

Then go to File and select Export C header file. This header file will export a text file that offers all the register values for this PLL. Then using the posted XMOS code, you can re-program the clock output value over I2C interface.

Suggest for you to consider this as your solution

a) if this external clock is fixed and you do not have any plans to change this value then the best solution is to apply a small footprint, low cost fixed SMD oscillator. From our last review, the 3225 SMD oscillator is the most practical due to the volume of sales. You should be paying around $0.30-$0.40 USD per oscillator in 1k pieces out of Shenzhen, CN. Check WTL as one quality vendor:

b) alternate options are to create a pierce oscillator using a local single gate buffer + a low cost crystal. However, from an automated production point of view, you will pay more in labor costs to stuff the xx # of parts for this discrete oscillator rather than the single placement cost for the complete SMD oscillator. Also, the PCB real estate will be larger for the discrete oscillator design. Something to note.

c) personally, we love the use of the Silabs Si5351A PLL which accepts a low cost 25 Mhz crystal (note that it is a crystal) and using I2C, you can dial up ANY clock you wish.

XMOS has already generated a fixed part with the same target clock output for audio projects:

https://www.digikey.com/products/en?key ... 4486-GT%20

If you purchase this exact p/n, CLK0 = 49.152 Mhz upon power up. No programming required.

You can find full source code for the use of the Si5351A PLL from here:

http://www.xcore.com/viewtopic.php?t=4647&start=10

NB: You only need the source code if you plan to change the power up value of this pre-programmed PLL. Otherwise, CLK0 will power up @ 49.152 Mhz.

The older clock builder tool is a gui tool -> select the 10 pin device -> select 25 Mhz crystal (we sourced these from WTL as well and are around $ 0.12 USD or lower) -> enter your target clock. Select Generate.

Then go to File and select Export C header file. This header file will export a text file that offers all the register values for this PLL. Then using the posted XMOS code, you can re-program the clock output value over I2C interface.

Suggest for you to consider this as your solution

-

xlordofpainx

- Experienced Member

- Posts: 78

- Joined: Thu Mar 08, 2018 2:44 pm

Great points. I will probably do exactly this (Silabs Si5351A PLL), looks quite clear and safe. Thanks again for the incredible advice.

-

mon2

- XCore Legend

- Posts: 1913

- Joined: Thu Jun 10, 2010 11:43 am

Wish to note that the posted source code for the XMOS CPU as I2C master (tested on StartKit but should be ok to use on any XMOS target kit) to configure the Si5351A is based on the (now) older Silabs Clock Builder tool. They recently upgraded the same tool but we have not yet validated the use and it appears the generated register values are quite different than the original release. Appears to be now bloatware - the original tool was very intuitive to use and we have applied this device on multiple designs with success.

The 10 pin package of this Si5351A is strictly requiring a local crystal (cannot use an oscillator). Also, you must inform the clock builder s/w of the ref crystal value using their pull-down menu. In error, we originally left at 27 Mhz and all of our desired clocks were skewed to be too low when confirming against external test equipment.

Download the (older) SiLabs configuration utility for this PLL from here:

http://www.silabs.com/Support%20Documen ... Si5351.zip

If you have a choice, select a 3225 size 25 Mhz crystal for this PLL. It should be the lower price point. We paid $ 0.074 USD (Shenzhen, CN) for this part but I recall that most offshore companies were in this range ($0.12 USD and lower). The Silabs part has internal caps so no external caps are required on the crystal legs.

The exact part we are using with our Si5351A PLL is:

The 10 pin package of this Si5351A is strictly requiring a local crystal (cannot use an oscillator). Also, you must inform the clock builder s/w of the ref crystal value using their pull-down menu. In error, we originally left at 27 Mhz and all of our desired clocks were skewed to be too low when confirming against external test equipment.

Download the (older) SiLabs configuration utility for this PLL from here:

http://www.silabs.com/Support%20Documen ... Si5351.zip

If you have a choice, select a 3225 size 25 Mhz crystal for this PLL. It should be the lower price point. We paid $ 0.074 USD (Shenzhen, CN) for this part but I recall that most offshore companies were in this range ($0.12 USD and lower). The Silabs part has internal caps so no external caps are required on the crystal legs.

The exact part we are using with our Si5351A PLL is:

-

xlordofpainx

- Experienced Member

- Posts: 78

- Joined: Thu Mar 08, 2018 2:44 pm

So - assuming that I have the right part. Is the following true: i will use the 24M for the XMOS and the 49.152 to another chip which will be processing I2S coming form the XMos. Is there a need for a sort of synching or will the 2 frequencies be synched to begin with, as they are coming from the same oscillator? There is Mclk Audio Mclk and SPdif Mclk, but these (depending on the options) are still the 24Mhz - would it be better to have these clockports take 49.152Mhz?

-

mon2

- XCore Legend

- Posts: 1913

- Joined: Thu Jun 10, 2010 11:43 am

Not being an audio person so here are some general comments:

1) definitely suggest that you consider the same PLL as the referenced p/n. Then there is "less to break". If it works in the XMOS ref design(s), then it should work for you. This device is available through Digikey and Mouser and is the programed version of the PLL defined by XMOS.

2) the same PLL is supported inside their IP over I2C so you are in good company to allow for configuration by factory s/w.

3) 24 Mhz is common to be used by the XMOS CPU (or a multiple of) so that the IP can accurately frame with USB packets.

4) the other clocks are for the audio codecs you will externally stitch to the XMOS processor. The datasheets for the codecs will most likely make use of the clock values generated by this PLL (or a multiple of).

For example, the 49.152 Mhz is the power up default of this PLL device but the I2C master code inside the XMOS Audio IP will dial up the registers to offer 49.152/2 as demanded by the installed codec.

NB: Have seen some offshore designs where the vendor bypasses the I2C driven PLL and just installs fixed SMD oscillators. Personally believe this is too restrictive and risky unless you have a proven working model already. You should find that the PLL + external 25 Mhz crystal will be around $ 1 to $1.50 USD total so worth the investment.

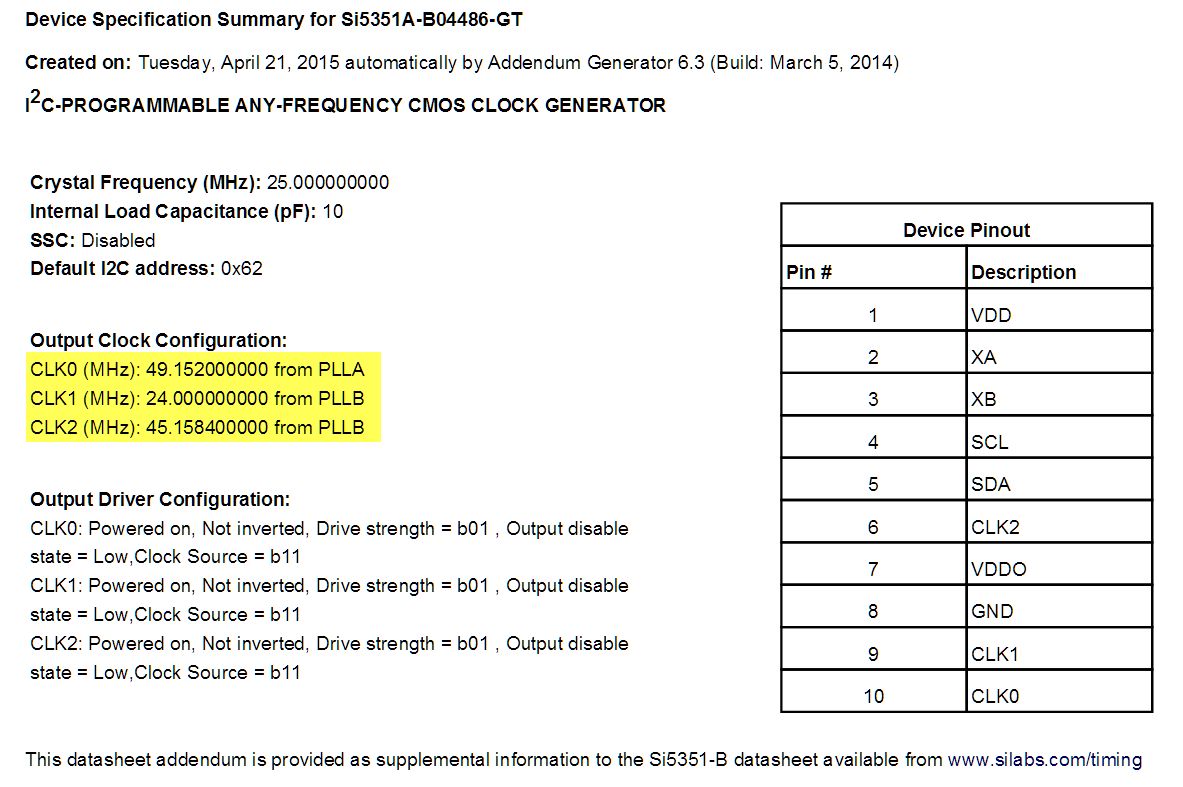

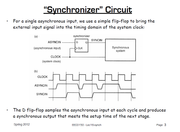

5) review the schematic of almost any XMOS audio design to observe how they make use of this PLL and external codec devices. For example, to sync the async SPDIF signal, an external flip-flop is applied- similar to the solution used by verilog / vhdl code programmers for fpga designs.

1) definitely suggest that you consider the same PLL as the referenced p/n. Then there is "less to break". If it works in the XMOS ref design(s), then it should work for you. This device is available through Digikey and Mouser and is the programed version of the PLL defined by XMOS.

2) the same PLL is supported inside their IP over I2C so you are in good company to allow for configuration by factory s/w.

3) 24 Mhz is common to be used by the XMOS CPU (or a multiple of) so that the IP can accurately frame with USB packets.

4) the other clocks are for the audio codecs you will externally stitch to the XMOS processor. The datasheets for the codecs will most likely make use of the clock values generated by this PLL (or a multiple of).

For example, the 49.152 Mhz is the power up default of this PLL device but the I2C master code inside the XMOS Audio IP will dial up the registers to offer 49.152/2 as demanded by the installed codec.

NB: Have seen some offshore designs where the vendor bypasses the I2C driven PLL and just installs fixed SMD oscillators. Personally believe this is too restrictive and risky unless you have a proven working model already. You should find that the PLL + external 25 Mhz crystal will be around $ 1 to $1.50 USD total so worth the investment.

5) review the schematic of almost any XMOS audio design to observe how they make use of this PLL and external codec devices. For example, to sync the async SPDIF signal, an external flip-flop is applied- similar to the solution used by verilog / vhdl code programmers for fpga designs.