I have a long-term hobby project, to build a robot that can do something that is very boring for a human - placing SMD components.

I have built a machine from scratch, including the electronics and software. Everything is open-source - but is work in progress.

So far, the explorer KIT has been used with different daughter cards connected to it.

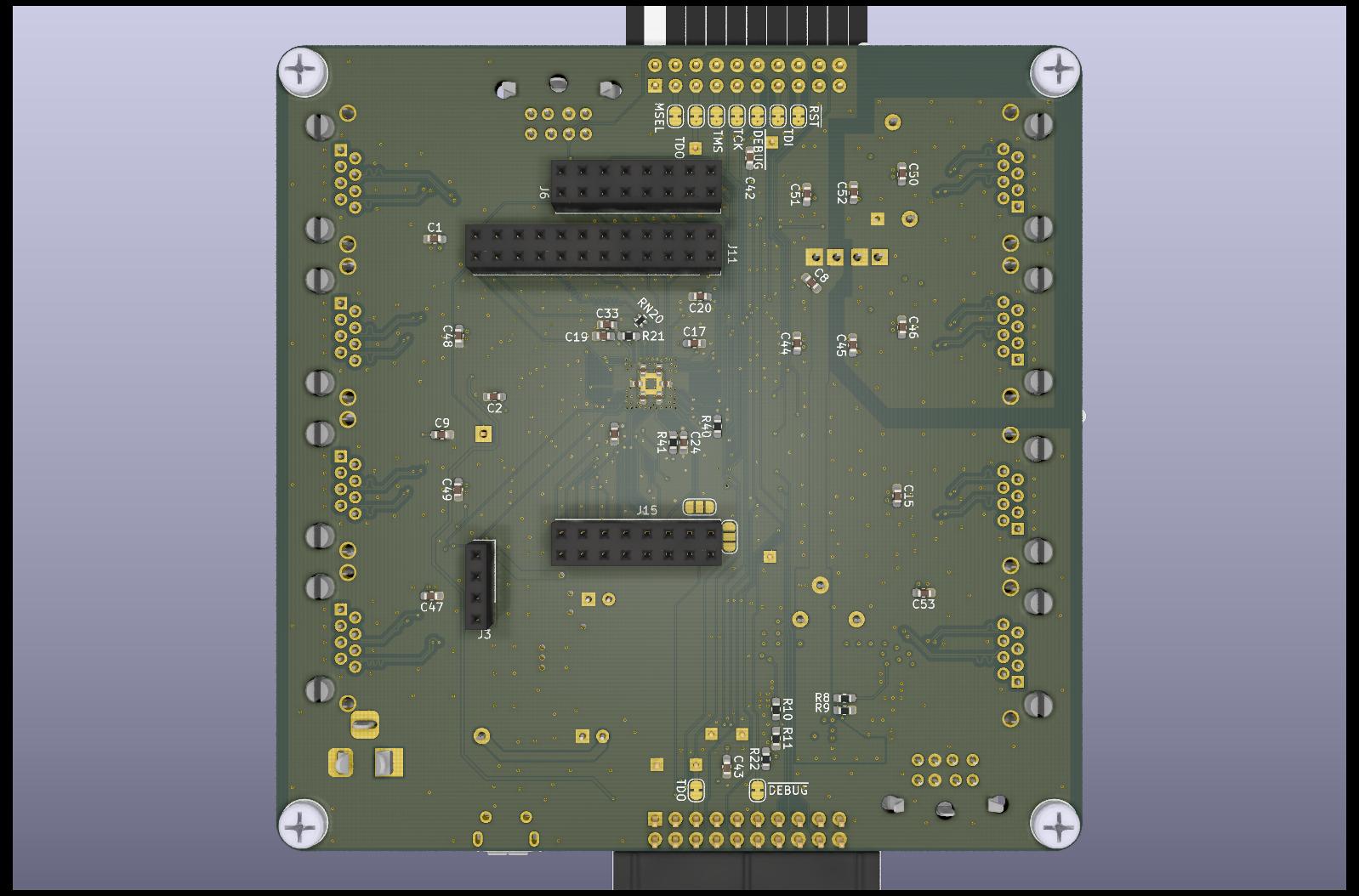

I would appreciate if someone could check my XTAG, Xlink connections etc. on the new "CPU" board. The board is intended to be connected in a galvanic isolated XLink network, for an example like this

https://github.com/lilltroll77/XMOS-XU2 ... etwork.pdf or

https://github.com/lilltroll77/XMOS-XU2 ... etwork.pdf

The networks above run in the xTIMEcomposer simulator without errors.

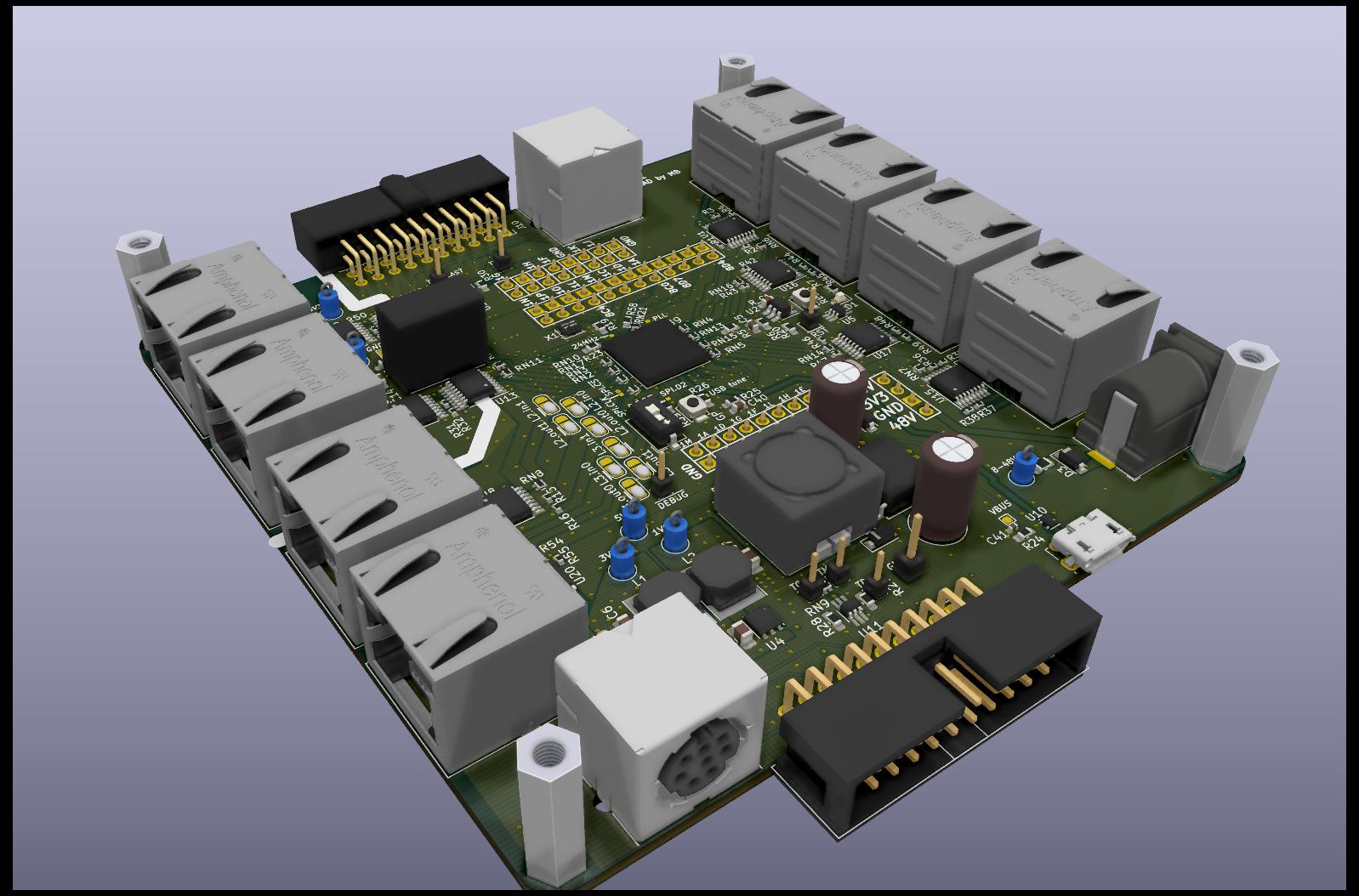

The PCB's can either be populated as a hub with USB, and a Gigabit ethernet shield, or as a network node that runs

FOC SVPWM for BLDC (Field-oriented control combined with Space Vector Pulse Width Modulation for Brushless DC Motors) by connecting a daughter card/shield power by the 48V motor rail.

USB ground will be isolated from power ground.

Schematic, board layout and virtual reality files can be found here.

https://github.com/lilltroll77/XMOS-XU216_FB236-BOARD

---------------------------------------------------------------------------

Here is an old video when using the eXplorer KIT + stepper motors + the machine itself.

https://www.youtube.com/watch?v=MYEp6bmtVj4

https://www.youtube.com/watch?v=U8llYMeUdWE

https://www.youtube.com/watch?v=jBj-VGELGH0

First BLDC version can be found here with eXplorer KIT.

https://workspace.circuitmaker.com/Proj ... put-driver

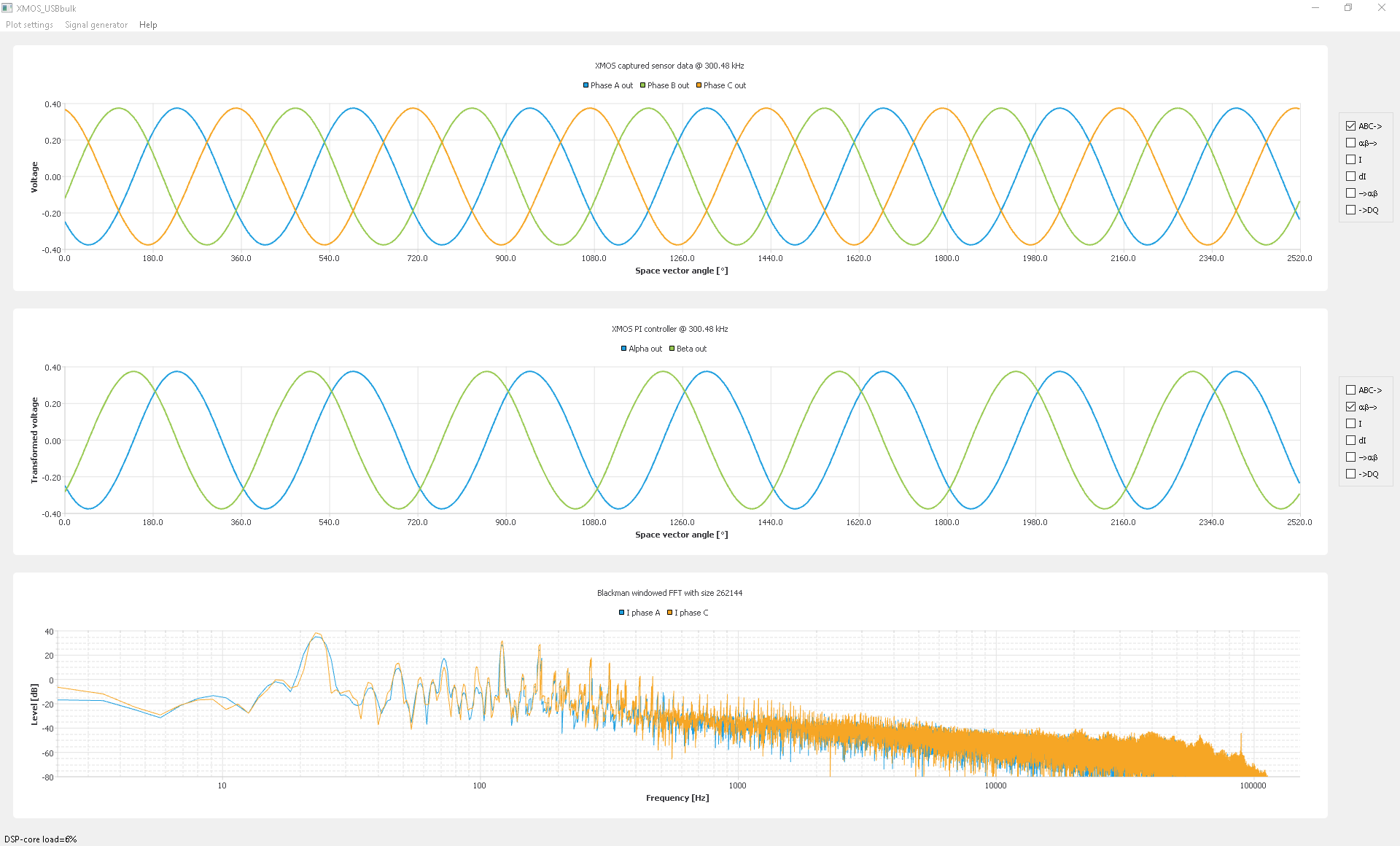

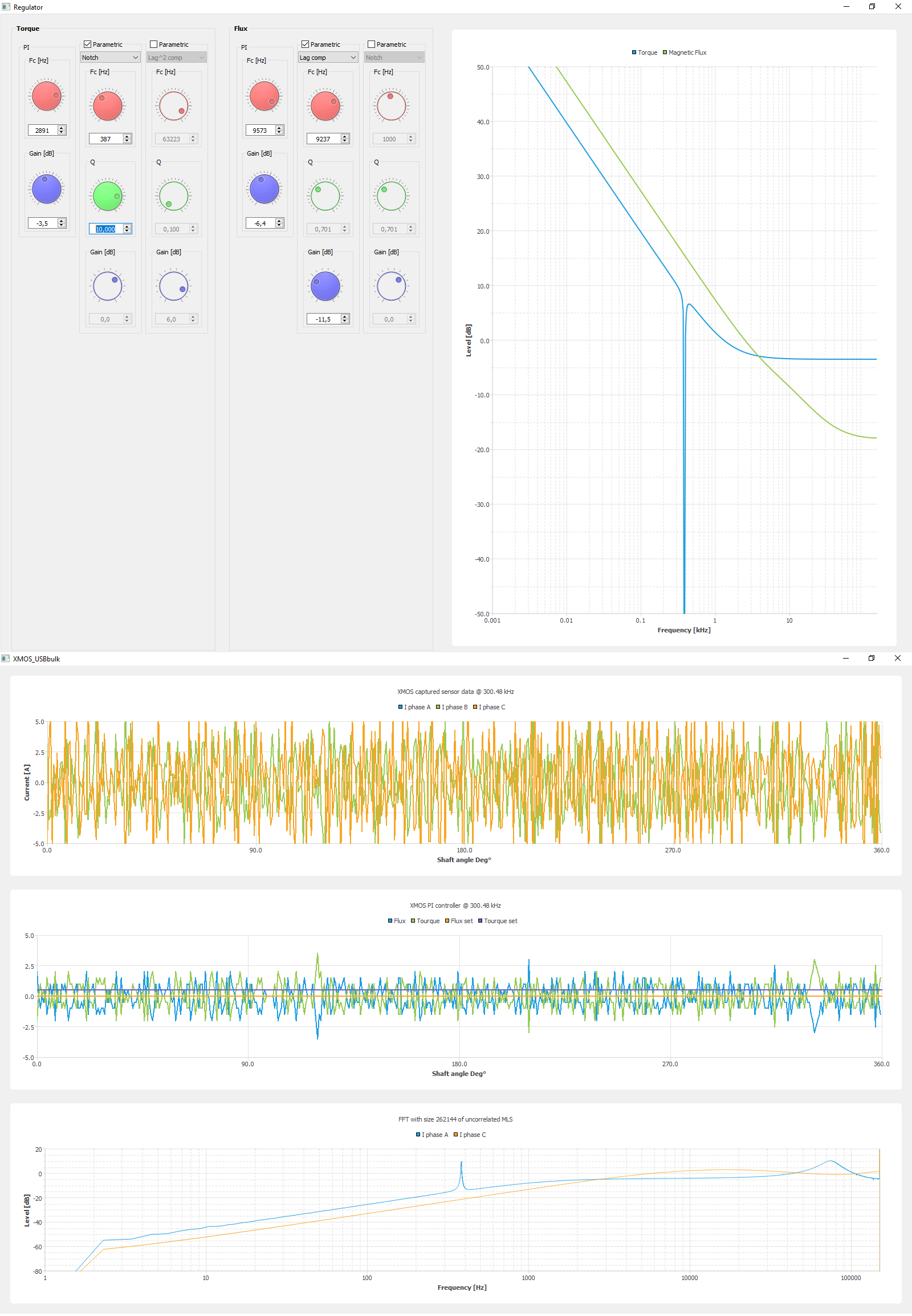

There is also a large GUI on the host side written in Qt (C++). Below is 2 early pictures. XMOS streams ~ 10Mbyte/s of controller real-time data to the host over a custom bulk USB driver.

GCODE for moving the robot is created by the http://openpnp.org/ software which also uses machine vision.